#

# D1.2 Report on intra-node and multi-node optimizations for HPC codes

| Contract Number      | 828947                                                                                                                                                                                                              |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project Website      | www.enerxico-project.eu                                                                                                                                                                                             |

| Contractual Deadline | Wednesday 30 <sup>th</sup> September, 2020                                                                                                                                                                          |

| Dissemination Level  | PU                                                                                                                                                                                                                  |

| Nature               | R                                                                                                                                                                                                                   |

| Authors              | Michael Bader(TUM), Jose M Domínguez Alonso (VIGO),<br>Albert Farrés (BSC), Okba Hamitou (ATOS),<br>Jaime Klapp (ININ), Soline Laforet (ATOS),<br>Rafael Mayo (CIEMAT), Anne Reinarz (TUM),<br>Sebastian Wolf (TUM) |

| Contributors         | Romain Brossier (UGA), Jean-Matthieu Gallard (TUM),<br>Pablo García Müller (CIEMAT), Stephan Jaure (ATOS)                                                                                                           |

| Keywords             | Exascale, intra-node, multi-node, optimization, HPC                                                                                                                                                                 |

# Document Information

Notice:

The research leading to these results has received funding from the European Union's Horizon 2020 Programme under the ENERXICO Project (www.enerxico-project.eu), grant agreement no 828947 and under the Mexican CONACYT-SENER-Hidrocarburos grant agreement B-S-69926.

C2020 ENERXICO Consortium Partners. All rights reserved.

| 1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                                                                          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2. | Highlights                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                          |

| 3. | ALYA         3.1. Performance and Scalability Assessment         3.2. Improvements to Performance and Scalability         3.2.1. Dynamic load balance         3.3. Summary and Outlook                                                                                                                                                                                                                                                          | 6<br>7<br>7<br>10                                                                                          |

| 4. | BSIT         4.1. Performance and Scalability Assessment         4.2. Improvements to Performance and Scalability         4.2.1. Optimise BSIT for Nvidia Volta GPU architectures         4.3. Summary and Outlook                                                                                                                                                                                                                              | <b>12</b><br>12<br>12<br>13<br>15                                                                          |

| 5. | <b>DualSPHysics</b> 5.1. The Black Hole (BH) Oil Reservoir simulation code.         5.2. POP CoE Performance Analysis         5.2.1. DualSPHysics Test Cases         5.2.2. DualSPHysics Parallel Efficiency         5.2.3. Analysing CUDA API and Kernels         5.2.4. Identified Performance Issues         5.2.5. Summary of the POP audit         5.3. Multi-GPU implementation of DualSPHysics: advances and implementation difficulties | <ol> <li>17</li> <li>17</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> </ol> |

| 6. | <b>ExaHyPE</b> 6.1. Performance and Scalability Assessment         6.2. Improvements to Performance and Scalability         6.3. Summary and Outlook                                                                                                                                                                                                                                                                                            | <b>22</b><br>22<br>23<br>26                                                                                |

| 7. | SeisSol         7.1. Performance and Scalability Assessment         7.2. Improvements to Performance and Scalability         7.2.1. Optimise SeisSol for non-Intel architectures         7.2.2. Evaluation of NUMA-aware MPI+OpenMP parallelisation         7.2.3. Evaluation of the computation performance on AMD Zen2 architecture         7.2.4. Performance engineering for model extension         7.3. Summary and Outlook               | <ul> <li>27</li> <li>28</li> <li>28</li> <li>30</li> <li>32</li> <li>33</li> <li>33</li> </ul>             |

| 8. | SEM46         8.1. Performance and Scalability Assessment         8.2. Improvements to Performance and Scalability         8.3. Summary and Outlook                                                                                                                                                                                                                                                                                             | <b>35</b><br>35<br>36<br>39                                                                                |

| 9. | WRF                                              | 40 |

|----|--------------------------------------------------|----|

|    | 9.1. Performance and scalability Assessment      | 40 |

|    | 9.2. Improvements to Performance and Scalability | 40 |

|    | 9.3. Summary and Outlook                         | 41 |

| Α. | Appendix                                         | 44 |

|    | A.1. ExaHyPE Setup for Zen2                      | 44 |

|    | A.2. Compiling and Running SeisSol               | 45 |

|    | A.3. Theoretical peak performance                | 50 |

| в. | POP Audit for DualSPHysics                       | 52 |

### 1. Introduction

This deliverable presents performance optimisations of all simulation software addressed within the ENERXICO project. It is the second of a series of three deliverables in ENERXICO's work package WP1 on "Exascale Enabling". It thus continues on Deliverable D1.1, in which the focus has been on performance and scalability assessment. Bottlenecks identified in the first deliverable are now being addressed by the ENERXICO researchers and first optimisations have been carried out.

For each code we will first summarise the findings of the performance assessment performed for Deliverable D1.1. Here we distinguish between the audits, which have been done in cooperation with the POP CoE, own performance measurements during the ENERXICO project and other assessments. We also point out further measurements that came up during the work on D1.2. For each exascale optimisation target we explain the strategy and report on work executed to improve performance and scalability, Performance measurements demonstrate respective achievements. Finally, we summarise the status of every code and lay out its progress on the road to exascale. In addition we point out further steps for the remaining project period.

## 2. Highlights

For each code we summarise the targets, which have been achieved in the ENERXICO project.

- **ALYA** One of the main goals was to improve the execution time in parallel runs by reducing the load imbalance found in some scenarios. By using the Dynamic Load Balancing Library (DLB) when simulating particle-dominated systems (10M of particles) we can achieve speed-ups up to  $3.5\times$ , reducing this improvement up to  $1.5\times$  for fluid-dominated systems (0.5M of particles).

- **BSIT** The objectives of the work were to optimise BSIT code for Nvidia Volta GPUs. We have implemented and evaluated the effect of some traditional approaches to improve finite difference codes in Volta GPUs, such as blocking, shared memory, register streaming and shuffle instructions. Our fully optimised code shows a speed-up of about  $2\times$  when compared with an unoptimised version. Furthermore, we obtain a speed-up of about  $3.5\times$  when compared with older accelerators like Intel Xeon Phi, and more than  $5\times$  when compared to state of the art HPC processors like Intel Xeon Scalable.

- **DualSPHysics** The POP CoE Performance and Scalability Analysis, which has been delayed for Deliverable 1.1, has now been completed. The extension of the code to multi-GPU is underway, we have important advances but we have encountered several difficulties that are related to architecture differences between old and new GPUs that are expected to be solved within the next few months. An update of the POP audit will then be necessary for the latest GPU architectures.

- **ExaHyPE** The objectives of the work were to port and perform scaling analysis on AMD Rome Zen2 architecture by taking into account the NUMA architecture. The scaling is performed on up to 11000 cores. By targeting AVX2 instruction sets, the optimised XSMM library achieves a speed up of 69% compared to a generic implementation of GEMM.

- **SeisSol** A major goal was to optimise SeisSol, which was originally targeted to Intel architectures, for AMD processors. We identified a more pronounced NUMA architecture as

major difference. By using NUMA aware parallelisation techniques we were able to achieve a speedup of  $\approx 26\%$  on AMD Rome architectures. The optimisations were also evaluated on Intel Skylake and achieved a speedup  $\approx 18\%$ .

- **SEM46** Following the results of the POP audit, the vectorisation enablings and improvement of the memory management allowed to achieve an 24% gain in the computational time in the isotropic approximation. For the next steps, these optimisation principles shall be carried out in the anisotropic approximation. The outcome shall be tested on a large scale test case to incite the communication optimisations already introduced.

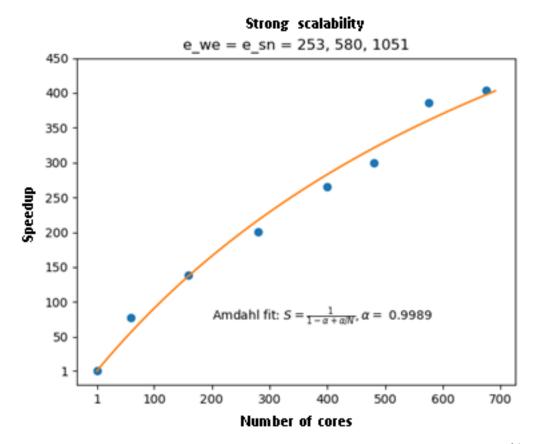

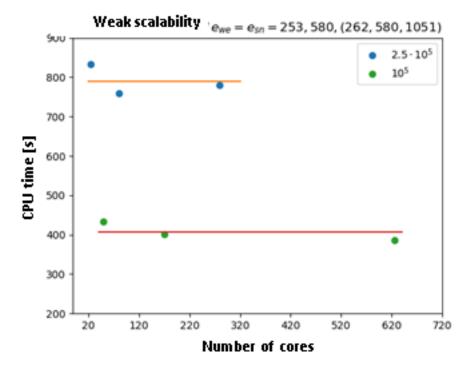

- **WRF** The objective of the work was to perform scaling analysis on the Intel Gold Architecture for identifying bottlenecks of the code. The analysis is made following the methodology defined by the POP CoE. It identified excessive communication calls that should be reduced. Strong and weak scaling tests have been performed on up to 675 cores. By reducing the aforementioned communication calls by introducing local variables in the modules of interest, speed up of 8% compared to a generic implementation of the previous version is achieved.

# 3. ALYA

Alya is a high-performance computational mechanics code to solve engineering coupled problems. The different physics solved by Alya are incompressible/compressible flow, solid mechanics, chemistry, particle transport, heat transfer, turbulence modelling, electrical propagation, among others.

Multiphysics coupling is achieved in a multi-code manner. MPI is used to communicate between the different instances of Alya, where each instance solves a particular physics, with the potential of performing asynchronous executions of the different physics. Alya is specially designed for massively parallel supercomputers.

**Goals in ENERXICO** In ENERXICO, we focus our efforts on improving Alya performance in the context of WP4 (biofuels for transportation), which develops and implements models required in the multiphysics code of Alya to investigate combustion processes of selected fuels.

The following table summarises the effort (in person months, PM) spent on WP1 until Month 16 of the project:

| Partner | PM spent |

|---------|----------|

| BSC     | 5        |

#### 3.1. Performance and Scalability Assessment

Alya implements different levels of parallelisation including MPI for distributed memory systems, OpenMP and OmpSs for shared memory [5] and GPU support among others. As far as the parallelisation is concerned, in this work we rely exclusively on MPI as this is the version used in production runs. The MPI parallelisation of Alya relies on Metis to partition the mesh in subdomains. It should be noted that contrary to classical implementations of the Finite Volume and Finite Difference methods, halo cells or halo nodes are not required to assemble the matrices or residuals in the Finite-Element method [9]. Avoiding duplicated work on these cells, provides a certain advantage in the assembly phase for the Finite-Element method, where the scalability only depends upon the control of the load balance.

The Alya benchmarks have been performed on systems with Intel Skylake architectures (JUWELS and MareNostrum4). MareNostrum4 is the Tier-0 system hosted by BSC, Spain. It is based on Intel Xeon Platinum processors from the Skylake generation. It is a Lenovo system composed of SD530 Compute Racks, an Intel Omni-Path high performance network interconnect and running SuSE Linux Enterprise Server as operating system. Its current LINPACK R max Performance is 6.2272 Pflop/s. This general-purpose block consists of 48 racks housing 3456 nodes with a grand total of 165,888 processor cores and 390 TB of main memory. JUWELS, the Jülich Wizard for European Leadership Science, is the Tier-0 system hosted by the Jülich Supercomputing Centre, Germany. JUWELS is an Atos Bull Sequana X1000 system with dual 24-core Intel Xeon Platinum 8168 (Skylake) CPUs @ 2.7 GHz and an EDR-InfiniBand. The peak performance is 9.89 Pflop/s.

**Benchmarking** We have tested a Alya with two test cases:

- **Test Case A.** A 132 million element mesh representing the flow around a sphere. It is expected to scale up to 1500 MPI tasks.

- **Test Case B.** A 1056 million element mesh representing the flow around a sphere. It is expected to scale up to 12000 MPI tasks.

The elapsed time of only the time-integration phase has been considered, since it is the dominant part in the production runs of Alya. Likewise, the node workload for each system was selected according to the similar configurations used in scientific simulations.

Table 1 and Table 2 present the results for the Skylake systems, JUWELS and MareNostrum4 for Case A and B respectively. We can observe better performance on JUWELS for all the cases because the CPU frequency on JUWELS (2.7 GHz) is higher than on MareNostrum4 (2.1 GHz).

| Number of cores | Time (s) | <b>Speedup</b><br>JUWELS | Efficiency | · · ·  | <b>Speedup</b><br>IareNostrum | •    |

|-----------------|----------|--------------------------|------------|--------|-------------------------------|------|

| 192             | 124.24   | 1.0                      | 100%       | 129.45 | 1.0                           | 100% |

| 384             | 62.56    | 2.0                      | 99%        | 67.45  | 1.9                           | 96%  |

| 768             | 31.24    | 4.0                      | 99%        | 33.93  | 3.8                           | 95%  |

| 1536            | 16.45    | 7.6                      | 94%        | 18.28  | 7.1                           | 89%  |

Table 1: Alya results for Test Case A running in Skylake architectures.

| Number of cores | Time (s) |        | Efficiency | · · ·  |             | Efficiency |

|-----------------|----------|--------|------------|--------|-------------|------------|

|                 |          | JUWELS |            | Ν      | IareNostrum | 4          |

| 1152            | 372.52   | 1.0    | 100%       | 451.38 | 1.0         | 100%       |

| 2304            | 196.48   | 1.9    | 95%        | 262.32 | 1.7         | 86%        |

| 4608            | 99.65    | 3.7    | 93%        | 124.98 | 3.6         | 90%        |

| 9216            | 61.34    | 6.1    | 76%        | 86.61  | 5.2         | 65%        |

Table 2: Alya results for Test Case B running in Skylake architectures.

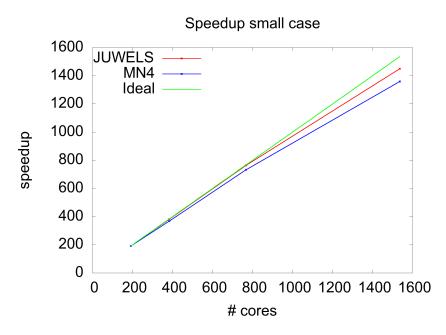

Figure 1 and Figure 2 shows the speedup results for the Skylake systems, JUWELS and MareNostrum4 for Case A and B respectively. We can observe that on all the cases is the speedup is better in JUWELS than for MareNostrum4. One of the causes of this difference on the efficiency is the network of each system, Mellanox EDR-InfiniBand on JUWELS and Intel Omni-Path on MareNostrum4.

#### 3.2. Improvements to Performance and Scalability

#### 3.2.1. Dynamic load balance

Lagrangian particle tracking is of great interest in engineering. In the literature, particle tracking is usually solved within the same code, after obtaining the solution of the Navier–Stokes equations. However, in a distributed memory context, it is very likely that particles are concentrated in very few MPI partitions, resulting in a very poor load balance. This work will thus address this issue: the dynamic load balance applied at the MPI level of parallelism.

**Synchronous and asynchronous couplings** In this work, we only consider a one-way coupling, which means that the particles are transported by the fluid but have negligible effects on the fluid dynamics. Two solutions will be analysed and compared. First, synchronous coupling using the same instance of the code, and thus the same subdomain partitioning for the fluid and the particles. Second, in order to gain asynchronism, the fluid to particle coupling is also achieved via a multi-code strategy using two instances of the Alya code. In this case, the fluid and particle

Figure 1: Alya speedup for Test Case A running in Skylake architectures vs Ideal speedup.

domains are partitioned independently, with a different number of subdomains. At the end of a time step, once the velocity and pressure of the fluid are obtained, the velocity field is sent to the particle subdomains, via the MPI\_ISend function.

In the particle code using the synchronous coupling strategy, the load is dramatically imbalanced, and in the worst case, all the particles may be in a single subdomain. Moreover, even if we were able to distribute the particles in a homogeneous manner, they will be migrating over time and may end up producing a load imbalance. On the other hand, when using the asynchronous coupling strategy, one must select the distribution of MPI processes between the fluid and particle codes. Moreover, as the load of the particles will change during the execution, the optimal distribution of MPI processes between fluid and particle codes can change as well.

To attack these problems, we implement a dynamic solution, which is applied at runtime, the Dynamic Load Balancing Library (DLB). DLB [4] is an independent and interoperable dynamic library that can help parallel applications improve their load balance. This library was developed and is actively maintained by the BSC Computer Science team. DLB is applied at runtime meaning that we do not need to analyse specific inputs or modify the application code. The philosophy of the library is to exploit the computational resources (i.e. CPUs or cores) of the MPI processes blocked in an MPI blocking call by other processes running on the same node, by spawning more threads of the second level of parallelism (i.e. in our case, OpenMP). When running with DLB, whenever an MPI process detects that it is not using its cores (i.e. it is waiting in a blocking MPI call), it will lend its resources to the system. Another process running on the same node can then use these cores and spawn more OpenMP threads to parallelise further the end of its computation.

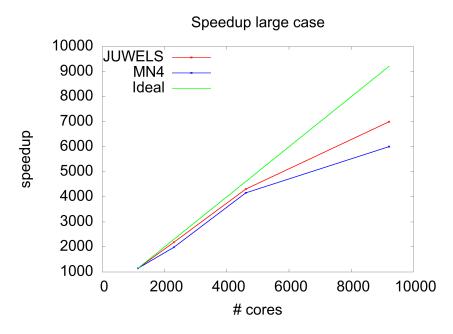

In Figure 3, we can see different traces of an execution of the Alya code with MPI processes and two OpenMP threads each. The X-axis represents time and each horizontal line is a thread (grouped by MPI process). In these traces, the blue colour represents computation of the fluid

Figure 2: Alya speedup for Test Case B running in Skylake architectures vs Ideal speedup.

code, the green represents computation of the particle code and the orange global communications (in black and white, from darker to lighter). The top image is the original execution, where we can clearly see the imbalance of the particle code, and less spectacular, but significant, we can see the imbalance of the fluid code. In the middle image, we can see the same execution with DLB. In the bottom figure, we show a zoom of one of the nodes (the most loaded one and consequently the bottleneck). We can see that when the particle code is running (green), only one MPI process have computation to perform, and all the other MPI processes are waiting in a global communication (orange). At this point, the process running the particles is able to use the 16 cores of the node, by spawning 16 OpenMP threads. The same observation can be made in the fluid code whenever imbalance is present.

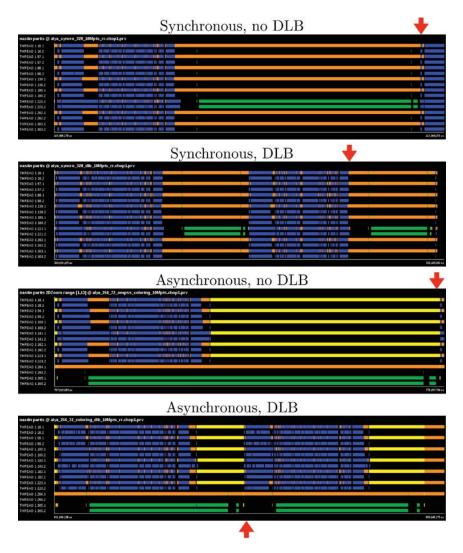

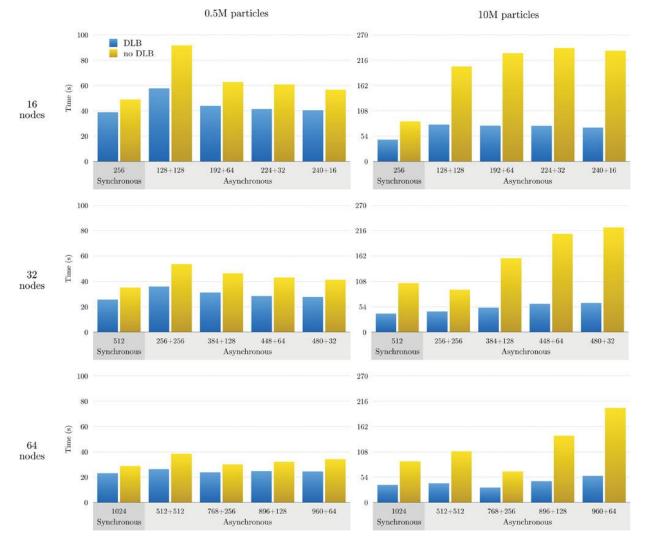

**Results** In Figure 4, we can see the average execution times for the different configurations. The first conclusion is that the performance, when the computation is dominated by the fluid (0.5M particles, left-hand side charts), differs from the one obtained by the particle-dominated execution (10M particles, right chart of the figure). This is due to the fact that the fluid and the particle codes have different scalability behaviours, i.e. while the fluid code scales quite well the particle code has a poor scalability due to the high load imbalance. Therefore, the global scalability highly depends on which code dominates the computation. We can see how DLB can help to improve the scalability by providing a better resource utilisation. When simulating 10M of particles, DLB can make the execution between a 45% and 72% faster (a speed-up between 1.8 and 3.5 with the same number of resources). When running with 0.5M of particles, DLB can run between 20% and 32% faster (a speed-up between 1.2 and 1.5 of the original code). When analysing the performance of the asynchronous version, we can see that it depends on the distribution of MPI processes among the fluids and the particles codes. Almost in all the cases, we can find a configuration of MPI processes that perform better than the synchronous version. But at the same time, when choosing any of the other configurations, we can see how the

Figure 3: Global Alya traces and zoom.

performance drops; for some of the configurations, the asynchronous code with a bad distribution can be two times slower than the synchronous one. Finally, we can observe that DLB is able to hide the performance problem when using a bad distribution of MPI processes among the codes (fluids and particles). The execution time when using DLB is almost constant independently of which version we are running (synchronous or asynchronous) and how many MPI processes for fluids and particles we are running.

#### 3.3. Summary and Outlook

We have implemented a dynamic load balance strategy to mitigate the uneven distribution of particles across the different MPI partitions. The dynamic load balance strategy equalises the execution times of all possible configurations between fluid and particle MPI processes, thus making the combination of MPI processes a less important decision from the user point of view. Moreover, using DLB when simulating particle-dominated systems (10M of particles) we can achieve speed-ups up to 3.5, reducing this improvement up to 1.5 for fluid-dominated systems (0.5M of particles).

Figure 4: Alya Timings. (From top to bottom: 16, 32, 64 nodes. (Left) 0.5M particles. (Right) 10M particles).

# 4. BSIT

BSIT is a software platform, designed and developed to fulfil the geophysical exploration needs for HPC applications. Geophysical exploration is a field that needs huge amounts of computational resources. BSIT was developed to cope with such needs, including different types of processing systems running over a wide range or HPC architectures. The main systems included in BSIT are forward modelling, reverse time migration and full waveform inversion. In addition, the software supports different rheologies including acoustic, acoustic with variable density, elastic, viscoelastic and electromagnetic. Moreover, several levels of anisotropy are supported: VTI/HTI, orthorhombic, TTI and arbitrary anisotropy (for elastic and viscoelastic rheologies).

**Goals in ENERXICO** In ENERXICO, we focus our efforts on improving BSIT performance in the context of WP3 (Oil and Gas), which explores and evaluates methods implemented by BSIT for realistic modelling scenarios proposed by the industrial partners of the project.

The following table summarises the effort (in person months, PM) spent on WP1 until Month 16 of the project:

| Partner | PM spent |

|---------|----------|

| BSC     | 5        |

#### 4.1. Performance and Scalability Assessment

**Known performance/scalability bottlenecks** Roofline analysis shows a low arithmetic intensity (common in stencil codes), GPU utilisation analysis confirms that performance is bounded by the memory system. The limiting factor is the bandwidth in device memory.

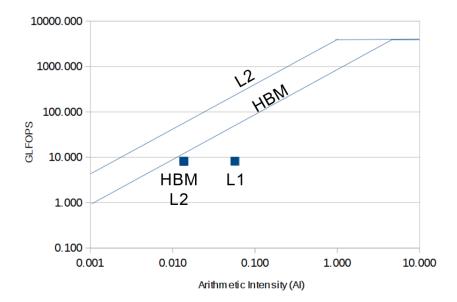

**Benchmarking** We use roofline analysis [17] to evaluate how well BSIT performs in terms of peak performance relative to the arithmetic intensity.

By using the roofline model, we provide an insight of our application behaviour placing its performance into a graphical representation bounded by both the maximum (attainable) performance FLOPS and the memory bandwidth. The model imposes a limit on the performance based on the operational intensity of an application, showing how much room exists for improvement.

Using a maximum bandwidth of 900 GB/s via HBM (High Bandwidth Memory) and 14000 GFLOPS as maximum Floating Point (FP) performance, we can infer that a minimum operational intensity of  $\sim 15.55$  FP operations/byte would be needed to take advantage of the total FP performance available in a Nvidia Volta GPU. Figure 5 depicts a roofline showing how close we get to the attainable performance for each memory level. Table 3 details the roofline data.

#### 4.2. Improvements to Performance and Scalability

**Implemented measures** L1 and L2 memory access should be improved to reuse data and increase the arithmetic intensity. If arithmetic intensity is increased there is room for a performance (GFLOPS) improvement. Also, efficiency can be increased by fixing data alignments and improving memory access patterns.

Stencil codes like BSIT are usually bounded by memory bandwidth. Improving performance relies on increasing arithmetic intensity so relative peak performance is increased too. Making a clever use of the different memories on the device as well improving memory access patterns can resolve in an overall improved performance.

Figure 5: Roofline of attainable performance for each memory level running on Nvidia Volta GPUs vs. the observed operational intensity.

| Memory level | Bandwidth<br>(GiB/s) | Arithmetic<br>Intensity<br>(flop/byte) | Achieved<br>performance<br>(GFLOPS) | Maximum<br>Bandwidth<br>(GiB/s) |

|--------------|----------------------|----------------------------------------|-------------------------------------|---------------------------------|

| HBM          | 598.12               | 0.014                                  | 8.165                               | 900                             |

| L2           | 595.60               | 0.014                                  | 8.165                               | 4200                            |

| L1           | 412.79               | 0.057                                  | 8.165                               | ??                              |

Table 3: Detailed performance data.

In general, achieving huge speed-ups is difficult for stencil memory bounded codes in modern HPC architectures. Consequently, we only expect minor speed-ups relative to the current optimised version of the code.

#### 4.2.1. Optimise BSIT for Nvidia Volta GPU architectures

When porting/re-implementing computational intensive kernels of code, users also face the decision to introduce hardware tailored optimisations that provide a most efficient version of the code compared to a base implementation that does not consider the architecture where the program will be running. We have implemented and evaluated the effect of some traditional approaches to improve finite difference codes in Volta GPUs separately and all together, such as blocking, shared memory, register streaming and shuffle instructions. We observe how each optimisation affects the throughput of the whole compute kernel and each of the costly regions of the algorithm. Additionally, we compare the performance obtained to the resulting throughput on the Power 9 processor to which Voltas are connected and other Intel-based HPC architectures. We show that with very few optimisations and the computing capacity of the Voltas, the overall obtained performance is higher compared with previous HPC hardware when evaluating finite differences codes.

Our base implementation is the direct result of developing a Finite Differences (FD) method over a Fully Staggered Grid [1] (FSG) grid. This will lead us to a loop in time where velocities are updated based on stresses values in odd iterations and the other way around for even iterations. To update velocities, 12 different 3D stencils plus another 12 3D material interpolations for each point of the grid must be calculated. Materials are stored in a single vertex of the FSG cell for memory saving issues, trading storage per computation. On the other hand, the computation involves 28 3D-stencils calculations plus 84 3D interpolations for the material properties to update stresses. Notice that both velocities and stresses calculations are typically dominated by accesses to global memory to retrieve the data needed to update the corresponding values. Our baseline version of the code shows the two innermost loops in space mapped to a 2D Cuda grid, streaming cells to update to each thread over the slowest dimension (Y), as seen in [14]. Thread block dimensions have not been tuned for Volta architecture. Our work studies the effect of the following optimisations applied to the baseline version, with the aim of improving the performance of FSG in NVIDIA Volta GPU cards:

- Y-dim blocking. Traditional approaches for finite differences codes in GPUs usually map 2D thread blocks into ZX planes (i.e., faster dimensions). Then, each thread is in charge to update velocities and stresses for the whole Y (slow) dimension. By adding an extra dimension to thread blocks and mapping it to the grid Y dimension, we increase the number of thread blocks created maximising the GPU utilisation.

- **Shared Memory.** In Volta architecture it is possible to set up the scratchpad memory in each SM as 128 kB of cache (hardware managed) or 96 KB shared (software managed, thread block-addressable) memory. By placing some common data in this memory, it is possible to enhance reuse while maximising the memory throughput per thread.

- **Register Streaming.** The concept of traversing the data volume in the slowest dimension can be used. By doing this, it is possible to keep the slowest dimension values in a set of registers and load only one value between iterations in the traverse direction. In our case, this is useful for the Y dimension. This approach is similar to that used by [13], with some differences to take into account: our algorithm is FSG whereas theirs is Simply Staggered Grid (SSG) (and thus, they consider a smaller number of variables), and they use a spacial order of 4 whereas ours is 8, which raises the number of registers required in the kernel.

- **Shuffle Instructions.** Efficient data exchange between threads within the same warp can be achieved by using shuffle instructions. Also, a shuffle instruction is faster than shared memory since it only requires one instruction versus three for shared memory (write, synchronise, read). Shuffle instructions can be used to exchange data between threads within the same warp when computing stencils in Z (fast) dimension.

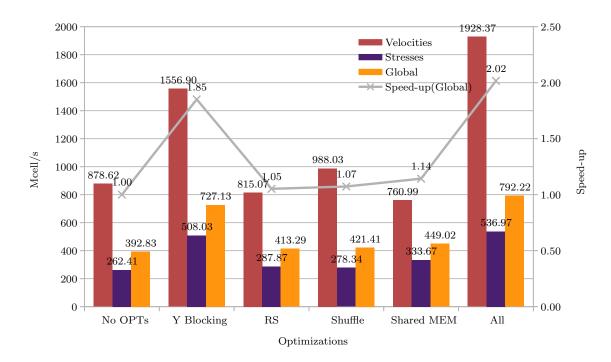

**Results** The proposed optimisations were implemented and evaluated for a computational grid built using FSG cells. Table 4 shows the environment used for the evaluation. Figure 6 depicts the achieved throughput on Volta architecture for all the proposed optimisations and the two different stages of the algorithm, the velocities and the stresses update, as well as the aggregated (denoted as *global*) throughput. The metric used is millions of cells per second (MCell/s). This is a typical throughput metric used for finite-difference kernels. It reports the rate at which the code can compute the required stencil formulas for each cell of the grid. MCell/s is an objective value that measures the actual performance of the problem independently of the architecture.

| System                                    | $4$ $\times$ GPU NVIDIA Tesla V100-SXM2 with 16GB HBM2                                |

|-------------------------------------------|---------------------------------------------------------------------------------------|

| Compiler                                  | NVIDIA CUDA Compiler 9.1.85                                                           |

| $\mathbf{CUDA}_{\mathbf{F}}\mathbf{LAGS}$ | -gencode arch=compute_ $35$ ,code=[sm_ $35$ ,sm_ $37$ ] -gencode arch=compute_ $50$ , |

|                                           | $code=sm_52$ -gencode arch=compute_70, code=[sm_70]                                   |

| Grid Size                                 | $128\times128\times128$                                                               |

Table 4: Evaluation environment specifications

Figure 6: FSG wave propagator throughput on one NVIDIA Volta V100 GPU.

The optimisations were enabled independently; thus the figures show the isolated effect of each optimisation. Besides, the achieved throughput enabling all optimisations at the same time is reported as *All*.

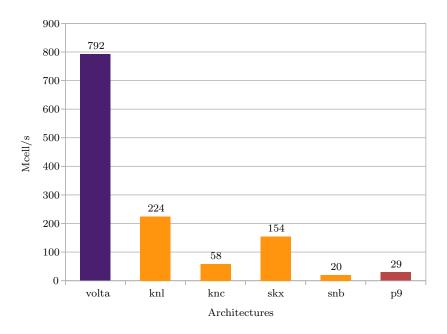

For additional reference, Figure 7 includes the performance of the same algorithm when optimised for the first and second generation  $\text{Intel}^{\mathbb{R}}$ Xeon  $\text{Phi}^{\text{TM}}$  processors (denoted in the Figure *knc* and *knl* respectively), as well as the performance obtained in the third and fourth iteration of the MareNostrum supercomputer (denoted *snb* and *skx* respectively). The performance achieved in the host processor, a dual socket IBM Power9 8335-GTG @ 3.00GHz with 20 cores, where Voltas GPU cards are attached is also reported as *p9*. It is worth mentioning that no effort has been put to optimise the algorithm for this last architecture.

#### 4.3. Summary and Outlook

We have shown a set of optimisations, applied to a Finite Difference Numerical method solving elastic wave propagation equations with support arbitrary anisotropy on NVIDIA Volta GPUs. The evaluated set of optimisations ranges from memory to compute optimisations. Our fully optimised code shows a speed-up of about  $2\times$  when compared with an unoptimized version. Furthermore, we obtain a speed-up of about  $3.5\times$  when compared with older accelerators like

Figure 7: Throughput architecture comparison.

Intel Xeon Phi, and more than  $5\times$  when compared to state of the art HPC processors like Intel Xeon Scalable.

## 5. DualSPHysics

DualSPHysics (https://dual.sphysics.org/) is a hardware accelerated Smoothed Particle Hydrodynamics code developed to solve free-surface flow problems. The code is developed to study free-surface flow phenomena where Eulerian methods can be difficult to apply, such as waves or impact of dam-breaks on off-shore structures. DualSPHysics is a set of C++, CUDA and Java codes designed to deal with real-life engineering problems.

DualSPHysics is an open-source code developed and released under the terms of GNU General Public License (GPLv3). Along with the source code, a complete documentation that makes easy the compilation and execution of the source files is also distributed. The code has been shown to be efficient and reliable. The parallel power computing of Graphics Computing Units (GPUs) is used to accelerate DualSPHysics by up to two orders of magnitude compared to the performance of the serial version.

#### 5.1. The Black Hole (BH) Oil Reservoir simulation code.

ENERXICO is developing a computer code called Black Hole (or BH code) for the numerical simulation of oil reservoirs, based on the numerical technique known as Smoothed Particle Hydrodynamics or SPH. This new code is an extension of the DualSPHysics code and is the first SPH based code that has been developed for the numerical simulation of oil reservoirs and has important benefits versus commercial codes based on other numerical techniques.

The BH code is a large-scale massively parallel reservoir simulator capable of performing simulations with billions of "particles" or fluid elements that represents the system under study. It contains improved multi-physics modules that automatically combine the effects of interrelated physical and chemical phenomena to accurately simulate in-situ recovery processes. This leads to the development of a graphical user interface multiple-platform application for code execution and visualisation, and for carrying out simulations with data provided by industrial partners and performing comparisons with available commercial packages. Furthermore, a large effort is being made to simplify the process of setting up the input for reservoir simulations from exploration data by means of a workflow fully integrated in our industrial partners' software environment.

An oil reservoir is composed of a porous medium with a multiphase fluid made of oil, gas, rock and other solids. The aim of the code is to simulate fluid flow in a porous medium, as well as the behaviour of the system at different pressures and temperatures. The tool should allow the reduction of uncertainties in the predictions that are carried out.

An oil reservoir system is very complex and a high resolution realistic simulation requires the use of up to one to ten thousand million particles. In one GPU we can simulate up to 200 millions particles, so a simulation with say one thousand million particles require the use of at least five GPUs or more depending upon the amount of particles that we load per GPU. An important part of this work is to produce a multi-GPU version of both the DualSPHysics and BH code that will allow us to perform high resolution simulations and to be prepared for the exascale technology. In section 5.3 we describe the initial stages towards this goal.

#### 5.2. POP CoE Performance Analysis

The single-GPU version of DualSPHysics was analysed as part of the parallel application performance assessment (Audit) service by the POP Centre of Excellence. Due to a delayed start of the "Mexican half" of the ENERXICO project, the POP Audit for DualSPHysics could only partly be provided in Deliverable 1.1 (as had been planned in the proposal). The audit has been finished in the meantime and results are reported in the remainder of this section – see also the respective POP report that is added in the appendix.

#### 5.2.1. DualSPHysics Test Cases

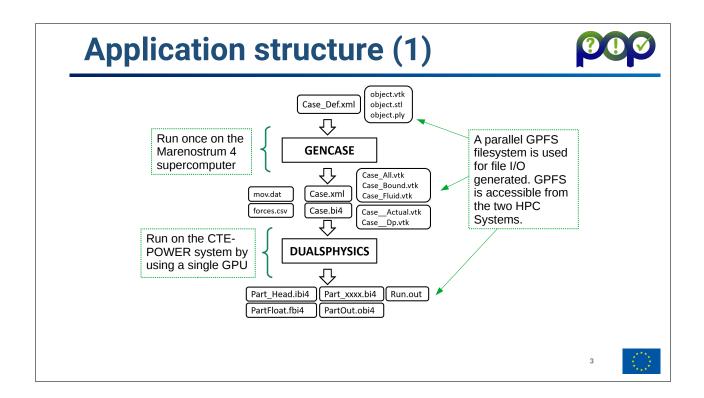

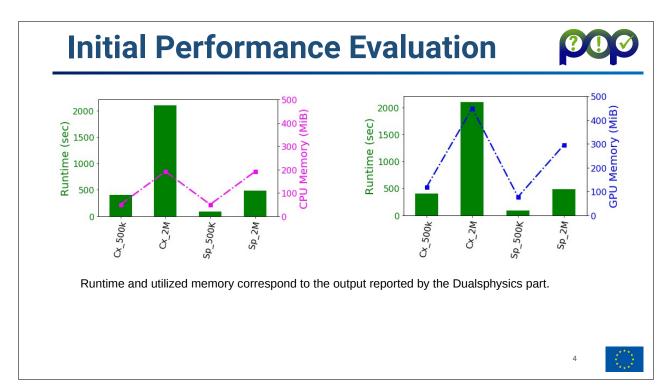

The test case is a very typical case in the Smoothed Particle Hydrodynamics (SPH) method that represents a Dam Break hitting a structure and that is frequently applied to compare performance. The test case was analysed for two numbers of particles and physics complexity doing a total of four different experiments. The number of particles selected are 500k and 2M; the physics complexity is denoted as Sp for the simplest physics and Cx with more complex physics. In this application, the simulation time depends mainly on the number of particles, the physical time to simulate and the physics applied.

Experiments were executed in the CTE-POWER HPC system at the Barcelona Supercomputing Center. The technical description of a compute node is as follows:

- Platform: CTE-POWER

- 2 x IBM Power9 8335-GTH @ 2.4GHz (3.0GHz on turbo, 20 cores and 4 threads/core, total 160 threads per node)

- 512GB of main memory

- 4 x GPU NVIDIA V100 (Volta) with 16GB HBM2

- Software: cuda-9.1+gcc-6.4.0

#### 5.2.2. DualSPHysics Parallel Efficiency

In the POP CoE, the parallel efficiency measures the parallel runtime impact on total execution time and this is composed by two sub-metrics – load balance and communication efficiency. Load balance is focused on the useful computation time per parallel task and the communication in the overhead produced by parallel runtime. In this case, the communication efficiency is related to operations like Scheduling/forkJoin and memory transfer (i.e. memcpy).

|                          | S      | р      | C      | 'x     |

|--------------------------|--------|--------|--------|--------|

| Efficiencies             | 500k   | 2M     | 500k   | 2M     |

| Parallel efficiency      | 35.89% | 46.98% | 38.15% | 47.63% |

| Load balance             | 70.88% | 59.73% | 65.49% | 56.82% |

| Communication efficiency | 50.64% | 78.66% | 58.25% | 83.82% |

Table 5: Single GPU Parallel Efficiency for DualSPHysics

This DualSPHysics version is at tracing level a parallel application with two parallel tasks. One task in the host and another in the GPU device. Therefore the efficiency metrics are measured as a work done by two parallel tasks. The parallel degree at CUDA level is done by using 3,196 grids and 128 blocks for the 500k cases and 13,745 grids and 128 blocks for the 2M cases. The number of GPU threads for 500k is 409,088 and 1,759,360 for 2M case, both for Sp and Cx complexity physic. However, the individual behaviour of GPU threads are not traced by the tool used in this Audit, but the whole behaviour on a GPU device is traced as a timeline for a parallel task.

Table 5 shows the efficiencies for the four cases analysed. As can be seen in Table 5, the load balance efficiency decreases from 500k to 2M for the Sp cases, because most computational

| State as is @ Case                                       | 50SP_200 | 90k_ct | e-pow | er.cho | p1.prv |     |      |       |       |       |        |       |           |

|----------------------------------------------------------|----------|--------|-------|--------|--------|-----|------|-------|-------|-------|--------|-------|-----------|

| THREAD 1.1.1                                             |          |        |       |        |        |     |      |       |       |       |        |       |           |

| CUDA-D1.S1-p9r1n15                                       |          |        |       |        |        |     |      |       |       |       |        |       |           |

|                                                          | 265,498, | 211 us |       |        |        |     |      |       |       |       |        | 265,6 | 87,918 u: |

| a) Running c                                             | ompu     | itati  | on (  | blue   | e) an  | d m | emoi | rv tr | ansfe | er (m | າສຸດອາ | nta)  | state     |

| CUDA memcpy size @                                       |          |        |       |        | ,      |     |      | - ,   |       | ) (II | lage   | iita) | brare     |

|                                                          |          |        |       |        | ,      |     |      |       |       |       |        |       | brace     |

| CUDA memcpy size @<br>THREAD 1.1.1<br>CUDA-D1.S1-p9r1n15 | Case5b   |        |       |        | ,      |     |      |       |       |       |        |       |           |

| THREAD 1.1.1                                             | Case5b   | Sp_200 |       |        | ,      |     |      |       |       |       |        |       | 87,918 u  |

(b) Transfer size for CUDA memcpy API. The green-blue scale bar at the bottom depicts the transfer size in bytes.

(c) CUDA Kernels. Brown colour corresponds to the KerInteractionForcesFluid kernel.

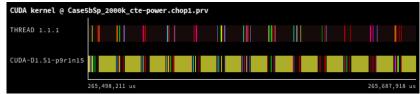

Figure 8: A paraver trace chop for Cx\_2M case. First timeline in each plot corresponds to task in the host and second timeline to the task in GPU device.

work is done at GPU level rather than in the host. Opposite behaviour can be observed for communication efficiency, because the time percentage for the memory transfer operations has less weight on 2M cases despite the absolute time increases about the 500k cases. Analysing the whole parallel efficiency, the values reported are low that is mainly related with memory transfer operations.

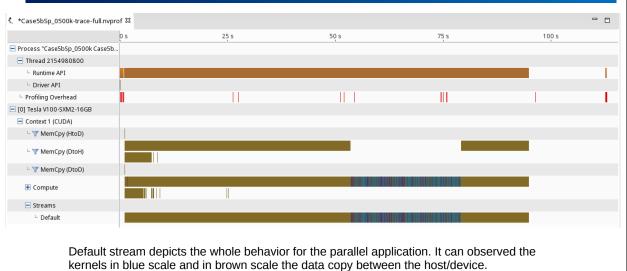

#### 5.2.3. Analysing CUDA API and Kernels

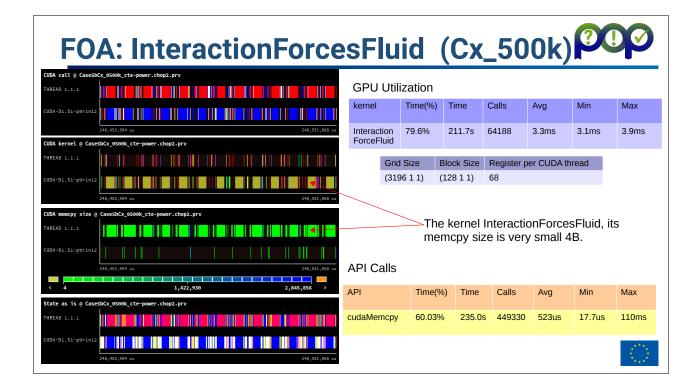

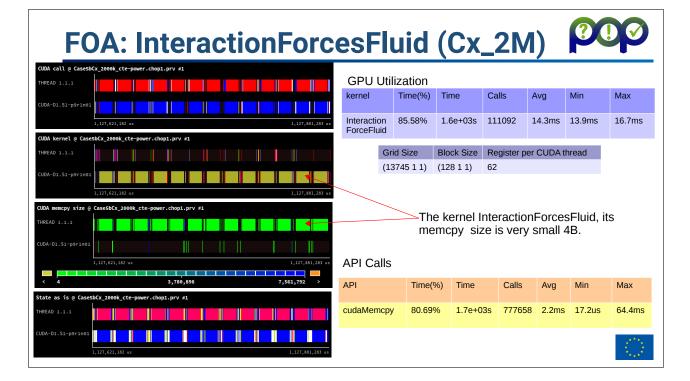

To identify the source of the poor efficiency reported in Table 5 a deeper analysis is done at CUDA kernels level and CUDA API. To do this, the **paraver** traces are analysed for the four cases. A **paraver** trace chop for 2M particles for Cx case is shown in Figure 8. As can be seen in Figure 8a, most of time the host task is doing memory transfer operations (in magenta colour) in small sizes of 4 bytes (green colour in Figure 8b) for the KerInteractionForcesFluid kernel (olive colour in Figure 8c), this behaviour is also observed for the others cases.

Table 6 shows the time percentage that the KerInteractionForcesFluid kernel represents in the kernels total time for the four cases. It can be observed that the number of particles has more impact on the percentage than the physic complexity and it is representing more than 70% about the all kernels total time.

Memory transfer time is mainly related with the CUDA API cudaMemcpy, in Table 7 the time percentage and count of calls are shown for the four cases. Over this percentage, the cudaMemcpy calls done from the host to the device during the running of KerInteractionForcesFluid kernel is around the 70% in the analysed cases.

Table 6: Timing and Calls for the KerInteractionForcesFluid kernel

| Case           | $\operatorname{Time}(\%)$ | Time                           | Calls       | Avg                | Min                | Max                 |

|----------------|---------------------------|--------------------------------|-------------|--------------------|--------------------|---------------------|

| $5bSp_0500k$   | 75.53%                    | 47.40s                         | $21,\!436$  | $2.21 \mathrm{ms}$ | 2.13ms             | $2.53 \mathrm{ms}$  |

| $5bSp_2000k$   | 83.14%                    | 339.38s                        | 35,461      | $9.57 \mathrm{ms}$ | $9.22 \mathrm{ms}$ | $10.90 \mathrm{ms}$ |

| $5bCx_0500k$   | 79.60%                    | 211.73s                        | 64,188      | $3.30\mathrm{ms}$  | $3.13 \mathrm{ms}$ | $3.94\mathrm{ms}$   |

| $5bCx_{2000k}$ | 85.58%                    | $1.6\mathrm{e}{+}03\mathrm{s}$ | $111,\!092$ | $14.30\mathrm{ms}$ | $13.87\mathrm{ms}$ | $16.67\mathrm{ms}$  |

Table 7: Timing for the API cudaMemcpy

|                |                           | 0                              |             |                      | 10       |                      |

|----------------|---------------------------|--------------------------------|-------------|----------------------|----------|----------------------|

| Case           | $\operatorname{Time}(\%)$ | Time                           | Calls       | Avg                  | Min      | Max                  |

| $5bSp_0500k$   | 60.13%                    | 53.98s                         | $128,\!631$ | 419.62 us            | 18.42us  | $4.56 \mathrm{ms}$   |

| $5bSp_2000k$   | 75.92%                    | 361.11s                        | 212,781     | $1.70 \mathrm{ms}$   | 17.38 us | $22.51 \mathrm{ms}$  |

| $5bCx_0500k$   | 60.03%                    | 235.00s                        | $449,\!330$ | $523.00 \mathrm{us}$ | 17.67 us | $110.32 \mathrm{ms}$ |

| $5bCx_{2000k}$ | 80.69%                    | $1.7\mathrm{e}{+}03\mathrm{s}$ | $777,\!658$ | $2.17 \mathrm{ms}$   | 17.22 us | $64.39 \mathrm{ms}$  |

#### 5.2.4. Identified Performance Issues

By analysing the obtained results, two main issues can be considered to improve the performance. On the one hand, the most logical step is to increase the parallelism degree by implementing a Multi-GPU version. On the other hand, a more complex analysis is required for the Ker-InteractionForcesFluid kernel that seems require a refactoring to increase the data transfer size between the host and the GPU devices. The impact of this kernel on the performance possibly could be reduced by using a Multi-GPU version without doing a refactoring of such kernel. However, the performance improvement can be greater by optimising the kernel implementation. The problem with this kernel is that each particle has to evaluate which surrounding particles are close enough and then calculate the interaction with each of them. This implies the use of several nested loops and divergence between the threads, because each thread calculates the values for a particle, but each particle interacts with different neighbouring particles and different numbers. This also leads to irregular memory access patterns and this requires a high volume of records that reduces the percentage of occupancy.

#### 5.2.5. Summary of the POP audit

In the final POP report (see apendix), the key findings were summarised as follows:

- The kernel KerInteractionForcesFluid represents more than 70% of the total kernels execution time.

- The kernel KerInteractionForcesFluid has more impact on the execution time in the four cases, due to the small data copied by memcpy API. This behaviour is similar for simple and complex physic cases.

- Computation time is less than 50 % of the total runtime for the four cases.

- CUDA memcpy is representing around the 60% of the execution time that is produced by the the kernel KerInteractionForcesFluid.

- Application's Kernel needs an additional refactoring to increase the degree of parallelism, it could be an Multi-GPU or explicit Streams programming.

# 5.3. Multi-GPU implementation of DualSPHysics: advances and implementation difficulties

The first multi-GPU approach of DualSPHysics was tested in the BSC (Barcelona Supercomputing Center BSC-CNS) in 2012 and the results were published in Domínguez et al. [3]. This multi-GPU version combines CUDA and MPI, where each MPI process handles one GPU. The division of the domain is done in one direction; therefore, each process usually only has to communicate with one or two neighbouring processes. The communication between processes is carried out through asynchronous sending of messages and synchronous reception to overlap communication and calculation times. In addition, it includes a dynamic load balancing to redistribute the particles after some time steps and minimise the synchronisation times between MPI processes. A more detailed description of the implementation and its results can be found in Domínguez et al. [2]. In 2013 an improved version was developed where CUDA streams, pinned memory and asynchronous transfers between CPU and GPU memory was used to improve the overlapping between communication and calculation times. This version was also tested in the BSC and the results were presented in the 8th International SPHERIC Workshop. The latest version improved the efficiency results of the previous version which were already very good. An efficiency close to 100% was achieved simulating 8 million particles per GPU on 128 GPUs Tesla M2090 of the MinoTauro GPU cluster of the BSC. The new efficiency tests are done in the CTE IBM Power9 cluster of the BSC. This cluster hosts 4 GPUs Tesla V100 per computation node. The software used in the tests carried out in the MinoTauro machine (see original specifications in Domínguez et al., [2]) is not available, so the improved multi-GPU version is compiled with the new software available in CTE-POWER cluster (CUDA 9.2, GCC 6.4.0 and Open MPI v3.0.0). Several problems were found when repeating the efficiency test in this cluster using the current software. Some code used for block size optimisation to run the CUDA kernels is not compatible with the new version of CUDA, so some changes had to be done to remove this code. The most important problem was that many simulations failed for different reasons and at different times. After considerable time and effort, it was found that the problem was in the communication with MPI. One MPI process sent some data, but the destination process received other data. This problem has already been discussed in some forums. There is some incompatibility between the use of pinned memory and MPI when this pinned memory allocated by CUDA is used in asynchronous message sending. The code was updated to detect this specific problem and also to avoid it. Finally, the corrected version was used to test the efficiency in the CTE-POWER cluster without any further failure. The efficiency test (weak scaling) was done up to 64 GPUs (the maximum allowed by the user account) simulating 4, 8 and 16 million particles per GPU. An efficiency of 91 % was achieved by simulating 8 and 16 million particles per GPU and 85% by simulating 4 million particles per GPU on 64 GPUs Tesla V100. The efficiency obtained is not bad, but it is less than the efficiency obtained in the MinoTauro cluster. There are important differences in software and hardware between the two efficiency tests. The most important difference is in the computational power of the GPUs Tesla V100 and Tesla M2090. The new GPU is almost 16 times faster than old GPU simulating the same testcase with 8 million particles, so the calculation time was drastically reduced while the communication time is similar.

# 6. ExaHyPE

The ExaHyPE engine solves systems of hyperbolic PDEs, as stemming from conservation laws. Models for seismic wave propagation problems, as addressed in ENERXICO's WP3 (Oil and Gas), have been developed within the ExaHyPE project (www.exahype.eu) and are being further developed in the ChEESE cluster of excellence (www.cheese-coe.eu). ExaHyPE is based on high-order Discontinuous Galerkin (DG) discretisation on tree-structured Cartesian meshes. For non-linear problems it offers an a-posteriori Finite-Volume limiter. Parallelisation of the ExaHyPE engine relies on the underlying Peano framework (www.peano-framework.org) for parallel adaptive mesh refinement. MPI is used for distributed-memory parallelism. Shared-memory parallelisation relies on Intel's Threading Building Blocks (TBB). The prime model for seismic wave propagation is based on the elastic wave equations on curvilinear meshes. It allows to simulate problems on suitably complicated geometry (topography, curved faults, e.g.) with a substantially reduced meshing overhead compared to approaches that work on unstructured grids.

**Goals in ENERXICO** ExaHyPE is a flagship code of the European Centre of Excellence ChEESE, which hosts the majority of activities to advance performance and scalability of ExaHyPE towards exascale (as for SeisSol, cmp. Section 7). In ENERXICO, we therefore focus on prototyping performance improvements for novel use cases of ExaHyPE in the context of WP3 (Oil and Gas), in particular towards inverse problems (Bayesian inversion) and uncertainty quantification. Additional activities towards "exascale enabling" (i.e., WP1) focused on collaboration opportunities within the consortium (TUM, BULL/ATOS, ...).

The following table summarises the effort (in person months, PM) spent on WP1 until Month 16 of the project:

| Partner   | PM spent |

|-----------|----------|

| TUM       | 3        |

| Bull/ATOS | 4        |

#### 6.1. Performance and Scalability Assessment

A POP audit for ExaHyPE has been attempted as part of the ChEESE CoE, before the start of ENERXICO. However, due to limited support of the POP toolset for Intel TBB, it was not possible to obtain audit results. We therefore did not attempt another POP audit in ENERX-ICO, but relied on performance assessments and findings identified in the ExaHyPE project. In addition, ATOS did a performance and scalability assessment in the first half of the ENERXICO project (cf. Deliverable 1.1).

#### Issues known since the start of the project:

- MPI Scaling: ExaHyPE relies on tree-structured grids and assigns subtrees to MPI ranks. This approach follows the Peano framework's original orientation towards multi-level and multi-grid problems. The subtree approach leads to a very coarse-grain load balancing, such that optimal scaling is only achieved at certain "sweet spots": the number of ranks should be related to powers of 3<sup>d</sup>, where d is the spatial dimension.

- **TBB Scaling:** TBB scaling depends strongly on the arithmetic intensity of the underlying models. For the linear elasticity model used in ENERXICO, scaling on Skylake nodes, e .g., drops significantly after 14 cores. These scaling limits result from a mixture of NUMA

effects, overheads of the task-based parallelisation approach and impact of sequential execution of the tree-oriented mesh traversals. The default strategy is therefore to work with multiple ranks per compute node.

#### Issues identified by ATOS during tests from D1.1

- Cache Stalls: A significant proportion of cycles ( $\approx 32$  %) are spent on data fetches from cache. The strategies adopted in the applications (data alignments ...) do not seem to work optimally. Such issues are related to intra-node parallelisation and therefore, the data sharing should be investigated in depth.

- MPI Time: The MPI time is high and represents almost 31% of the elapsed time. It is highly used by the MPI function "Iprobe" which is a non-blocking test for messages. Such problem may be caused by a non-optimal communication schema. On the other hand, it is shown that there is no MPI imbalance issue. Here, a dedicated rank is in charge of performing the load balance. Therefore, a big portion of time is spent in synchronisations.

- Vectorisation: A significant fraction of floating-point arithmetic instructions (93 %) are scalar and do not benefit from the advanced vectorisation capabilities of the processor. Only a small portion of the code is vectorised (≈7%) using AVX512 instruction set. This is due to the generic kernels employed in this test. In the optimized kernels a very high vectorisation level is reached.

Of these issues some arise only when using the generic (non-optimised) kernel variants of Exa-HyPE. The issues regarding cache-stalls and vectorisation have been resolved in the ChEESE-CoE for the linear applications of ExaHyPE.

**Benchmarking** ATOS has used Intel's advisor to benchmark ExaHyPE and to ensure comparability of the results we will continue to use Intel Advisor to measure, e.g. vectorisation levels. For MPI scaling we use internal tools to measure run-times.

#### 6.2. Improvements to Performance and Scalability

**Port to Peano4** The issue with MPI scaling only being available at certain "sweet spots" is caused by the underlying AMR framework Peano, which follows a tree-oriented scheduling of subgrids with the tree-structured adaptive Cartesian meshes, which may lead to large granularity of partitions. The new version Peano4 is developed by the group of Tobias Weinzierl at Durham University and should become available during the project period. It is designed to at least partially resolves these issues. We are therefore, in collaboration with Durham, rewriting the necessary interfaces in ExaHyPE to use Peano4. Initially we have focused on the Euler equations and low-order discretisations. As Peano4 develops further, we will enable more of ExaHyPE's features. While we do not see a speedup for the current sweet spots of the code by moving to Peano4, we see a considerable improvement away from the sweet spots.

**Multiple runs for UQ** ExaHyPE features a multi-solver interface that can be used to combine multiple solves on overlapping or non-overlapping meshes, also including different discretisation orders or even different PDEs. We will implement a multi-solver variant of our Multi-Level Markov-Chain Monte Carlo (MLMCMC) algorithm and intend to use ExaHyPE's multi-solver feature to improve overall runtime. The multi-solver interface will allow us to solve on every level

simultaneously. In very small test setups, we see that ExaHyPE's performance has reached the strong-scaling limit, by grouping multiple runs into one, we can avoid this and gain a speedup. The MLMCMC tests in ExaHyPE are in very early stages and considerable performance improvements are expected.

**Prototyping low and mixed precision in ExaHyPE** For inverse problems and UQ scenarios, it is often sufficient to execute entire simulations or at least certain performance-critical kernels in lower precision. We therefore examined the potential of exploiting low or mixed precision in ExaHyPE. We prototypically implemented a mixed-precision ADER-DG scheme that computes the element-local space-time predictor in single precision, but keeps double precision for the remaining calculation. We observed speedups of up to 60% for the space-time-predictor kernel, which for the not fully compute-bound elastic wave propagation scheme improved time-to-solution by roughly 30%. However, we also found that extending the prototype to a proper integration of mixed precision in the engine would require extensive changes in the ExaHyPE Toolkit and Kernel Generator, which is not feasible with the resources available in ENERXICO. Massive work would particularly be required in the algorithm layer, which is hard-coded in double precision and implements the ADER-DG scheme on the tree-structured adaptive grids provided by the Peano framework. Similar effort would be required for allowing to switch the general target precision between single and double precision.

Testing GEMM backends in ExaHyPE Many of ExaHyPE's element-local kernels are tensor operations, which can be computed as sequences of loops over matrix multiplications ("loop over gemm"). For best-possible performance of these small, fixed-size matrix multiplications, we rely on the LIBXSMM library [8] on Intel architectures. We updated the ExaHyPE Kernel Generator to also use the Eigen library (http://eigen.tuxfamily.org/) as matrix multiplication backend, which has previously shown promising results with SeisSol on ARM architectures. However, tests on the Intel Haswell architecture revealed that Eigen did not lead to performance advantages compared to a generic loop-based implementations. We will evaluate the issue more closely also on other architectures, but assume that the comparably small matrix sizes for the seismic use cases in ExaHyPE are already efficiently captured by a generic loop-based implementation. Still, the integration of the Eigen library has prepared the Kernel Generator for including other small-GEMM backends, which might be specialised for architecture like ARM, RISC V or similar.

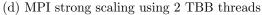

**Testing of ExaHyPE on the AMD Zen2 architecture** Tests on the AMD zen2 architecture have been performed using the ExaHyPE version which implements several types of GEMM backends. The "generic" GEMM backend uses non-optimised kernels. The "optimised" GEMM backend used the vectorised XSMM library. the latter is compiled targeting the AVX2 instruction set. The "optimised" backend can be combined with two other features: "split\_ck" which allows a better utilisation of the cache and "vectorise\_terms" which enables aggressive vectorisation.

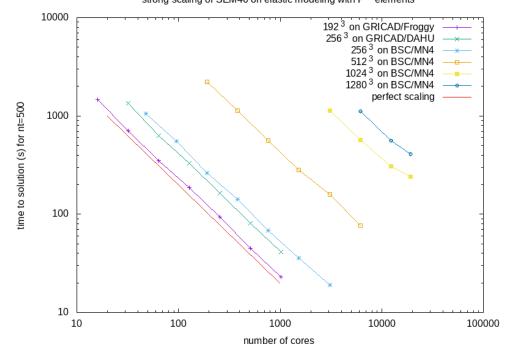

The test case used is a high order discontinuous Galerkin solver for elastic wave equation using a curvilinear mesh as it is described in appendix A.1. We simulate 100 time steps of the benchmark and measure MPI and TBB strong scaling. Following the recommendations of the POP audit, order 7 is used as because of its best performance.

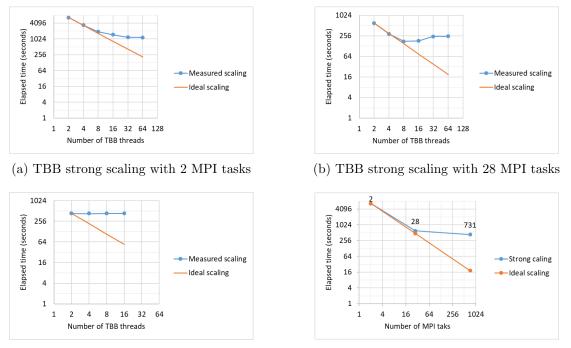

In Figure 9, the strong scaling analysis is performed for both shared memory parallelisation though TBB and distributed memory with MPI. Peano's geometrical domain-decomposition has load balancing sweet-spots at 2, 28 and 731 ranks. The best scaling is obtained via hybrid

(MPI+TBB) parallelism by exploit MPI sweet spots and increasing the number of TBB threads per MPI rank.

(c) TBB strong scaling with 731 MPI tasks

Figure 9: TBB and MPI strong scaling curves for ExaHyPE. The optimised LIBXSMM backend is used. The elapsed time is plotted using a logarithmic scale.

In Figure 9a, Figure 9b and Figure 9c, the number of TBB threads is increased starting from 2 to 64 TBB threads for each MPI sweet sport 2, 28 and 731. In figure Figure 9d, an MPI strong scaling is presented. In the latter, two TBB threads are used.

These results are in agreement with previous audits performed on ExaHyPE on Intel Skylake processors.

Figure 10: Performance comparison for generic and several level of optimisation in ExaHyPE. The tests are performed using 28 MPI tasks and the number of TBB threads varies from 2 to 16. The elapsed time is plotted using a logarithmic scale.

ExaHyPE shows great performance when using optimised kernels. The shared memory scalability is however limited when the number of threads reaches 16.

#### 6.3. Summary and Outlook

The ExaHyPE application has been successfully ported to the new AMD Rome architecture. The use of different backends, namely generic and several levels of optimised backend using LIBXSMM, has proven to be a good design decision as it is easy to switch to a new architecture. All further activities, especially the port to Peano 4, will be continued in the remaining project period, so we refer to the next Deliverable 1.3.

# 7. SeisSol

SeisSol is a software package for simulating seismic wave propagation and earthquake dynamics based on the discontinuous Galerkin method with arbitrary high-order derivative time-stepping (ADER-DG). Characteristics of the SeisSol simulation software are:

- use of arbitrarily high approximation order in time and space (ADER-DG with Godunov flux formulation) with the option for cluster-wise local time stepping.

- use of tetrahedral meshes to approximate complex 3D model geometries (faults & topography) for rapid model generation.

- use of elastic, anisotropic, viscoelastic and viscoplastic material to approximate realistic geological subsurface properties.

- parallel geo-information input (ASAGI).

**Goals in ENERXICO** SeisSol is a flagship code of the European Centre of Excellence ChEESE (www.cheese-coe.eu), which hosts the majority of activities to advance performance and scalability of SeisSol towards exascale (including particularly a port to GPU architectures). In EN-ERXICO, we therefore put a stronger focus on enabling novel use cases of SeisSol in the context of WP3 (Oil and Gas), which contains the extension towards further material models (anisotropic and poroelastic materials) and towards inverse problems. Additional activities towards "exascale enabling" (i.e., WP1) focused on collaboration opportunities within the consortium.

The following table summarizes the effort (in person months, PM) spent on WP1 until Month 16 of the project:

| Partner   | PM spent |

|-----------|----------|

| TUM       | 3        |

| Bull/ATOS | 4        |

#### 7.1. Performance and Scalability Assessment

SeisSol scales up to beyond-petascale supercomputers: extreme-scale simulations have been performed on several of the world's largest supercomputers in the past, for example on Tianhe-2 (8000 nodes accelerated by Intel's Xeon Phi co-processor; achieved 8.6 PetaFlop/s in double precision [7]) or on Cori (6144 nodes Xeon Phi "Knights Landing" CPUs;  $\approx 6$  PetaFlop/s in double precision, follow-up work to [16]).

In terms of single-core performance, the optimisation of SeisSol has been strongly oriented towards Intel architectures (Knights Corner/Landing; recently Skylake). The MPI+OpenMP strategy strived to rely on a single MPI rank per node to reduce the stress on MPI parallelism. A key algorithmic challenge to scalability is SeisSol's cluster-wise local time stepping, for which elements with a similar time step bound<sup>1</sup> are merged into cluster's, which are propagated in a multi-rate fashion. In the strong-scaling limit, small sizes of such clusters impede shared- and distributed-memory scalability. However, local time stepping is crucial for many scenarios that feature strong adaptive mesh refinement and/or highly complicated geometries and typically leads to strongly improved time-to-solution compared to global time stepping, despite losses in parallel efficiency.

<sup>&</sup>lt;sup>1</sup>from the Courant-Friedrich-Levy condition

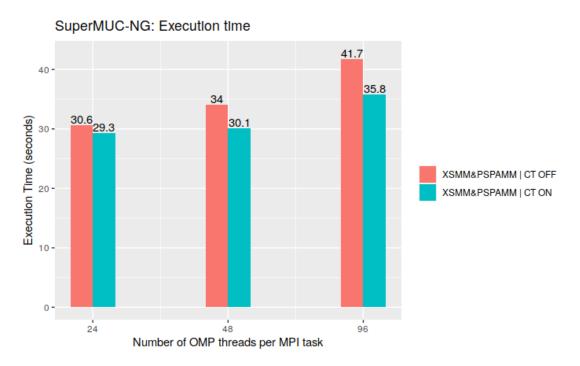

As part of the project, we had registered for an "extreme scaling workshop" at Leibniz Supercomputing Centre, for which full-machine runs on the SuperMUC-NG supercomputer (Intel Skylake CPUs, 26.8 PetaFlop/s theoretical peak) were envisaged. This workshop has been postponed to October 2020 due to the COVID-19 outbreak.

#### 7.2. Improvements to Performance and Scalability

#### 7.2.1. Optimise SeisSol for non-Intel architectures

Since AMD architectures are becoming more important (see, e.g., recent installations such as Hawk at HLRS Stuttgart, Mahti at CSC Finland or El Capitan at Lawrence Livermore), we evaluated SeisSol on these architectures.

**Hardware description** The technical analysis and experiments made for the application Seis-Sol, were executed by the applicative experts from the Atos Center of Excellence for Performance Programming (CEPP) team. The SeisSol application has been run on ATOS on-premise supercomputers. The specifics of these supercomputers are described in Figure 11.

|              | Atos Supercomputers                 |                                    |                            |                                    |  |  |

|--------------|-------------------------------------|------------------------------------|----------------------------|------------------------------------|--|--|

|              |                                     | Ge                                 | Genji                      |                                    |  |  |

|              | Processor SKU                       | AMD <sup>®</sup> EPYC <sup>®</sup> | Intel® Xeon®               | AMD <sup>®</sup> EPYC <sup>®</sup> |  |  |

|              |                                     | 7702                               | Gold 6148                  | 7742                               |  |  |

|              | Processor class                     | Rome                               | Skylake-SP                 | Rome                               |  |  |

| þ            | Fab Process                         | 7 nm                               | 14 nm                      | 7 nm                               |  |  |

| Processor    | TDP                                 | 200 W                              | 150 W                      | 225 W                              |  |  |

| ĕ            | Core Frequency (nominal)            | 2.0                                | 2.4                        | 2.25                               |  |  |

| •            | Cores per socket                    | 64                                 | 20                         | 64                                 |  |  |

|              | Processors per node                 | 2                                  | 2                          | 2                                  |  |  |

|              | Max. instruction set<br>supported   | AVX-2                              | AVX-512                    | AVX-2                              |  |  |

|              | DP FLOP/cycle                       | 16                                 | 32                         | 16                                 |  |  |

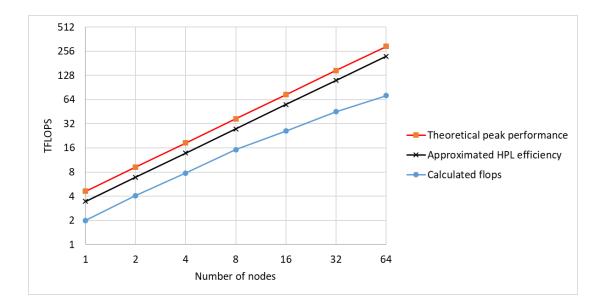

|              | DP GFLOPS/node<br>(theoretical)     | 4096                               | 3072                       | 4608                               |  |  |

| >            | Memory channels per<br>socket       | 8                                  | 6                          | 8                                  |  |  |

| Memory       | Memory DIMMs                        | DDR4 3200<br>MT/s                  | DDR4 3200<br>MT/s          | DDR4 3200<br>MT/s                  |  |  |

| 2            | Memory configuration (per<br>node)  | 8x 16GB (DR)                       | 187 GB                     | 256 GB                             |  |  |

|              | High Speed Interconnect             | Mellanox<br>ConnectX-5             | Mellanox<br>ConnectX-5     | Mellanox<br>ConnectX-5             |  |  |

| onnect       | Max Speed                           | 4x EDR<br>(100 Gbps)               | 4x EDR<br>(100 Gbps)       | 4x EDR<br>(100 Gbps)               |  |  |

| Interconnect | Topology                            | Fat-Tree<br>(Clos Network)         | Fat-Tree<br>(Clos Network) | Fat-Tree<br>(Clos Network)         |  |  |

|              | Oversubscription ratio<br>(typical) | 1:2                                | 1:2                        | 1:2                                |  |  |

Figure 11: Description of ATOS supercomputers.

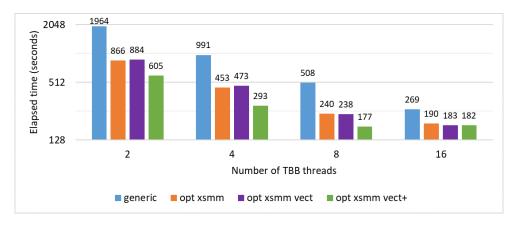

**Software environment and test case description** The SeisSol version used is the latest development version available in the master branch on the SeisSol Github. We used the community benchmark SCEC TPV13 [6] to compare different setups. The mesh consisted of 52 million elements. Computations have been run with convergence order 6. This test case describes a

spontaneous rupture on a 60-degree dipping normal fault in a homogeneous half-space (see Figure 12). A further detailed description of the test case is given in the reference document of

Figure 12: Diagram of the geometry of TPV13. 60-degree dipping normal fault.

SeisSol (https://seissol.readthedocs.io/en/latest/tpv13.html). An in-detail description of how we compiled and run SeisSol can be found in appendix A.2.

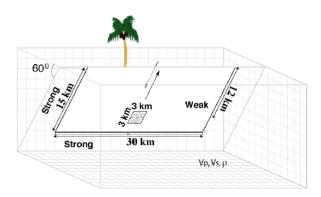

**Testing backends for Matrix Matrix multiplications (GEMM)** SeisSol uses the code generator YATeTo [15] for high-performance implementation of element-local operations. YATeTo allows expressing element-local operations on small tensors via a DSL, and maps these tensor operations to backends which perform Generalised Matrix Matrix multiplications (GEMM). For Haswell we use libxsmm (https://github.com/hfp/libxsmm) and for Skylake a combination of libxsmm and PSpaMM (https://github.com/peterwauligmann/PSpaMM).

We evaluated several code generator libraries for their suitability for AMD architectures.

As a target platform we used the cluster Spartan, which is located at ATOS. The AMD section of the cluster consists of 224 nodes each equipped with two AMD Rome EPYC 7742 with 128 cores/node as it is described in Figure 11.

The AMD Rome processors implement the Zen2 microarchitecture, which is similar to Intel's Haswell architecture. Hence the code generator libxsmm is a natural candidate for the Zen2 architecture. In addition we used the linear algebra library Eigen3 (eigen.tuxfamily.org/) as backend and Intel's MKL (https://software.intel.com/content/www/us/en/develop/tools/math-kernel-library.html).

Considering the backends for small matrix matrix multiplications, we identify libxsmm to be superior over the other candidates. Although libxsmm targets Intel architectures, we see that libxsmm configured for Haswell achieves good intra node performance on AMD Zen2 architecture. As PSpaMM makes use of AVX-512 instructions, it is not beneficial to combine it with libxsmm on the AMD Zen2 microarchitecture. Intel's MKL library is targeted at Intel architectures, but can also be compiled for AMD targeting AVX2 instruction set. It is known that Intel MKL performs bad on non Intel architectures. We just included it for the sake of completeness. Although we had considerable success with Eigen3 on ARM architectures, it did not live up to its expectations on AMD.

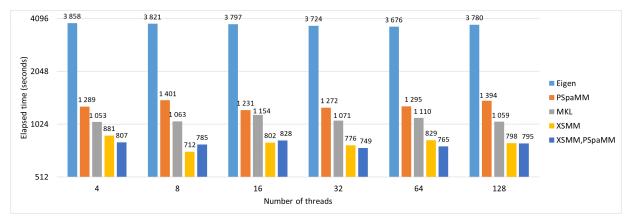

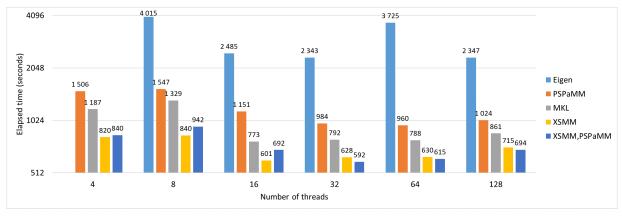

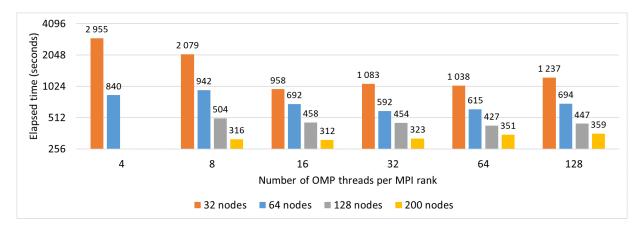

In Figure 13, for each backend, all 128 cores of one node are used. The number of MPI tasks and OMP threads vary such that all cores are used. For each run, 64 nodes are used.

**Remark.** *Time metric:* The relevant execution time is mentioned in the log file at the line containing the string "Elapsed time (via clock\_gettime):".

(a) Communication thread enabled

(b) Communication thread disabled

Figure 13: Comparison of the Eigen, MKL, XSMM, PSPaMM and XSMM, PSpaMM backends on 64 nodes runs. Labels on top of the bars denote the elapsed time in seconds.

#### 7.2.2. Evaluation of NUMA-aware MPI+OpenMP parallelisation